边缘端PCB测试加工项目询价公告

武汉数字化设计与制造创新中心有限公司以询价采购方式进行以下项目的采购,欢迎符合相应资格条件的供应商提交报价文件。

一、项目名称:__边缘端PCB测试加工___

二、采购预算:_____9.8万元_____

三、报价截止时间及报价文件递交地点:

1、报价截止时间: 自公告之日起5个工作日内

2、报价电子版递交邮箱: liyunhan@niiddm.com; weichuxuan@niiddm.com(同时发送,邮件主题格式为“《 》项目报价-XXX公司”<全称>)

四、采购项目内容及要求:

(一)采购项目一览表(示例)

|

序号 |

项目名称 |

项目研制的内容 |

备注 |

预算总价/元 |

|

1 |

边缘端PCB设计 |

边缘端PCB文件设计 |

|

98000 |

|

2 |

边缘端PCB加工 |

边缘端PCB加工与焊接 |

||

|

3 |

边缘端PCB电器性能测试 |

边缘端PCB上电测试 |

备注:(1)

说明:

1、本项目为整体采购,报价供应商应对所有项目做出响应,不允许部分报价。

2、交货地点: 武汉市东湖新技术开发区里沟南路8号武汉数字化设计与制造创新中心有限公司 。

3、交货期:以上全部产品须在 2021 年 11 月 20 日前交付,实际交付时间以我司验收合格日期为准。

4、付款方式: 项目验收交付合格后支付所有款项 。

5、产品质保期:质保期为1年,从乙方将产品交付给甲方且经甲方验收合格之日起计算。

五、报价供应商的资格要求:

1、报价供应商应具有独立的法人资格,相应的经营范围,并提供经年检的法人营业执照(副本)及税务登记证副本有效复印件。

2、为保护采购人的利益,保证本次供货产品是原厂商、正规渠道的产品,报价供应商应提供报价产品的代理、经销证书或针对本项目的专项授权书等有效证明文件(证明文件应具有可追溯性,报价供应商为报价产品制造商的除外)。

3、报价供应商必须提供法定代表人对报价供应商代表的授权书原件(报价供应商代表不是法定代表人的)及报价供应商代表的身份证复印件。

4、报价供应商必须提供至少一项涵盖本次报价全部同等规格设备的类似业绩证明,仅限订单合同或中标通知书,如单项业绩证明无法覆盖全部报价设备的,须提供多项业绩证明。业绩证明材料须能够明确全部同等设备的价值。

六、报价要求

1、总报价为货物送达采购人指定地点,经采购人验收合格并交货完毕所有可能发生的费用,包括设备费、运输、保险费、采购保管、安装、产品检验检测、操作人员培训、税收、售后服务及采购代理服务等费用。

2、供应商对每一种货物(服务)只能有一个报价,供应商应在报价截止时间前报出不可更改的报价。

3、本项目的采购预算为报价的最高限价,报价超过采购预算的为无效报价。

七、成交供应商的确定原则:根据符合采购需求、质量和服务相等且报价最低的原则确定成交供应商。

八、其他事宜

1、分散采购小组在评审时将对供应商进行资格性和符合性检查。接受供应商的报价文件,并不意味着供应商的资格实质性符合采购要求。

2.供应商提供正式报价(格式自拟),如报价未提供明确偏离情况说明,无论是否做出书面承诺,均视为对上述报价要求无条件接受。

3、联系方式:

电话: 13487077030 ,联系人: 魏楚轩 。

地址:武汉东湖新技术开发区未来一路与里沟南路交汇处国家数字化设计与制造创新中心5楼

武汉数字化设计与制造创新中心有限公司

2021年 10月28 日

附件1 PCB设计技术要求表

|

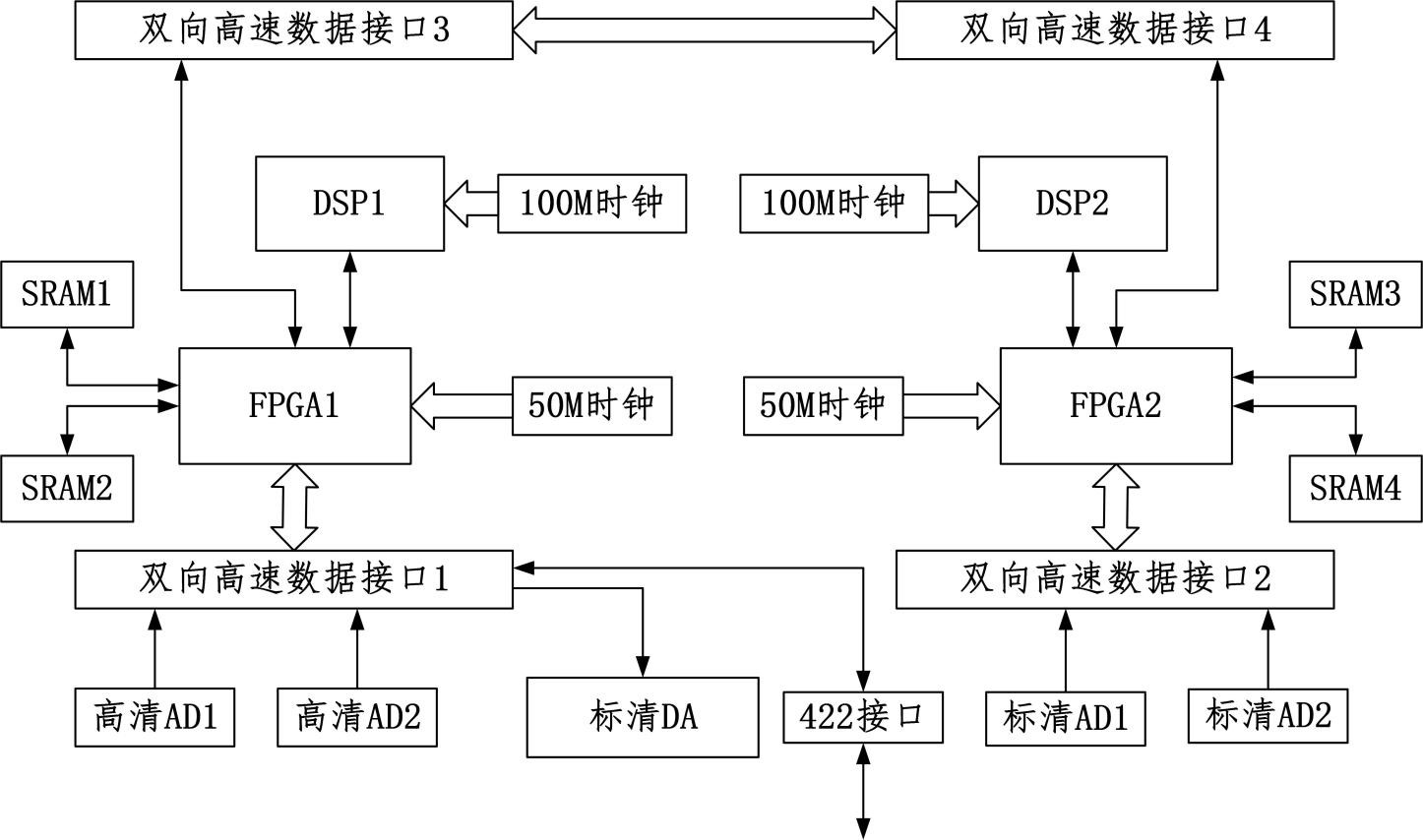

一、功能框图 (说明重要信号流向)

|

||||||||||||||||||||||||

|

三、信号说明 3.1 422串口信号 接收信号: VCR_INA_CANUART VCR_INB_CANUART 发送信号: VCR_OUTY_CANUART VCR_OUTZ_CANUART

3.2 双向高速数据接口1(主要数据)

|

||||||||||||||||||||||||

|

3.3 双向高速数据接口2(主要数据)

3.4 双向高速数据接口3、4(FPGA1与FPGA2主要通过此双向接口传输数据)

|

||||||||||||||||||||||||

|

3.5 SRAM与FPGA主要数据接口(以一个为例,其他类似)

3.6 FPGA与DSP主要数据接口(以一个为例)

四、系统时钟 FPGA(50MHz) DSP(100MHz)

|